## Verification of hardware dependent software

Submitted for the candidature of the degree of Doctor of Philosophy Department of Computer Science

Author: Supervisor: Ramsay G. Taylor Professor John Derrick

17th January 2012

ii

#### Abstract

Many good processes exist for ensuring the integrity of software systems. Some are analysis processes that seek to confirm that certain properties hold for the system, and these rely on the ability to infer a correct model of the behaviour of the software. To ensure that such inference is possible many high-integrity systems are written in "safe" language subsets that restrict the program to constructs whose behaviour is sufficiently abstract and well defined that it can be determined independent of the execution environment. This necessarily prevents any assumptions about the system hardware, but consequently makes it impossible to use these techniques on software that must interact with the hardware, such as device drivers.

This thesis addresses this shortcoming by taking the opposite approach: if the analyst accepts absolute hardware dependence that the analysis will only be valid for a particular target system: the hardware that the driver is intended to control — then the specification of the system can be used to infer the behaviour of the software that interacts with it. An analysis process is developed that operates on disassembled executable files and formal system specifications to produce CSP-OZ formal models of the software's behaviour. This analysis process is implemented in a prototype called Spurinna, that is then used in conjunction with the verification tools Z2SAL, the SAL suite, and IsabelleHOL, to demonstrate the verification of properties of the software. iv

## Declaration

I declare that this thesis was composed entirely by myself and that the work contained herein is my own except where explicitly stated otherwise. This work has not been submitted for any degree or professional qualification other than as specified.

## Ramsay Taylor

vi

# Contents

| 1 | Intr              | oduction 1                                                                 |  |

|---|-------------------|----------------------------------------------------------------------------|--|

|   | 1.1               | Motivation 1                                                               |  |

|   | 1.2               | Objective of this work                                                     |  |

|   | 1.3               | Thesis Outline                                                             |  |

| 2 | Baa               | kground 5                                                                  |  |

| 4 | 2.1               | Introduction                                                               |  |

|   | $\frac{2.1}{2.2}$ | Verification                                                               |  |

|   | $\frac{2.2}{2.3}$ | Code analysis   6                                                          |  |

|   | 2.0               | 2.3.1         Overview         6                                           |  |

|   |                   | 2.3.1         Overview         6           2.3.2         MISRA C         7 |  |

|   |                   | 2.3.3         SPARK Ada         8                                          |  |

|   |                   | 2.3.4       Hardware verification       9                                  |  |

|   |                   | 2.3.5         Summary         9                                            |  |

|   | 2.4               | Modeling         10                                                        |  |

|   | 2.1               | 2.4.1 Overview                                                             |  |

|   |                   | 2.4.2         The Z notation         11                                    |  |

|   |                   | 2.4.3 B                                                                    |  |

|   |                   | 2.4.4 CSP                                                                  |  |

|   |                   | 2.4.5 Object Z                                                             |  |

|   |                   | 2.4.6 CSP-OZ                                                               |  |

|   |                   | 2.4.7 Summary                                                              |  |

|   | 2.5               | Property verification                                                      |  |

|   |                   | 2.5.1 Overview                                                             |  |

|   |                   | 2.5.2 Hoare logic                                                          |  |

|   |                   | 2.5.3 Separation logic                                                     |  |

|   |                   | 2.5.4 IsabelleHOL                                                          |  |

|   |                   | 2.5.5 SAL                                                                  |  |

|   |                   | 2.5.6 Z2SAL                                                                |  |

|   |                   | 2.5.7 Summary                                                              |  |

| CC       | )N    | Т | EI | V | TS |

|----------|-------|---|----|---|----|

| $\sim c$ | / I I | - |    | • | LN |

| 3        | The  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1              | <b>27</b> |

|----------|------|------------------------------------------------------|-----------|

|          | 3.1  | Introduction                                         | 27        |

|          | 3.2  | The analysis process                                 | 27        |

|          | 3.3  | Formal model                                         | 28        |

|          |      | 3.3.1 System state specification                     | 29        |

|          |      | 3.3.2 Sequential instruction specifications          | 30        |

|          |      | 3.3.3 Branch instruction set specification           | 34        |

|          | 3.4  | Automated inference                                  | 38        |

| 4        | Sepa | aration in Z                                         | 41        |

|          | 4.1  | Overview                                             | 41        |

|          | 4.2  | Introduction                                         | 41        |

|          | 4.3  | Basic case                                           | 42        |

|          | 4.4  | A relaxation of the basic case                       | 44        |

|          | 4.5  | A simple function case                               | 46        |

|          | 4.6  | A simple relational case                             | 51        |

|          | 4.7  | Conclusion                                           | 52        |

|          | 1.1  |                                                      | 02        |

| <b>5</b> |      | <i>v</i>                                             | 53        |

|          | 5.1  | Disassembly                                          | 53        |

|          |      | 5.1.1 Overview                                       | 53        |

|          |      | 5.1.2 Executable files, object code, and disassembly | 53        |

|          |      | 5.1.3 Parsing                                        | 57        |

|          |      | 5.1.4 Summary                                        | 59        |

|          | 5.2  | Branch Identification                                | 59        |

|          |      | 5.2.1 Overview                                       | 59        |

|          |      | 5.2.2 Branch instructions                            | 59        |

|          |      | 5.2.3 Branch template format                         | 60        |

|          |      | 5.2.4 Example                                        | 61        |

|          |      | 5.2.5 Summary                                        | 64        |

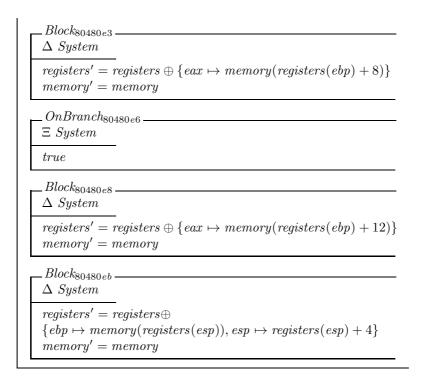

|          | 5.3  | Formal Instantiation                                 | 64        |

|          |      | 5.3.1 Overview                                       | 64        |

|          |      | 5.3.2 Template specifications                        | 64        |

|          |      | 5.3.3 Instantiation                                  | 67        |

|          |      | 5.3.4 Summary                                        | 67        |

|          | 5.4  | Simplification                                       | 68        |

|          | 0.1  | 5.4.1 Overview                                       | 68        |

|          |      |                                                      | 68        |

|          |      | 5.4.3 Algorithm                                      | 69        |

|          |      | 5.4.4 Summary                                        | 69        |

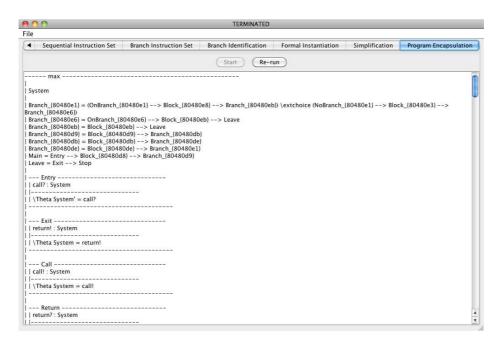

|          | 5.5  | Program Encapsulation                                | 70        |

|          | 0.0  | 5.5.1 Overview                                       | 70<br>70  |

|          |      |                                                      |           |

|          |      |                                                      | 70<br>71  |

|          |      | 5.5.3 Function calls                                 | 71        |

|          |      | 5.5.4 Class definition                               | 72<br>79  |

|          |      | 5.5.5 Summary                                        | 72        |

## viii

## CONTENTS

| 6  | The          | Spurinna implementation                                           | <b>73</b> |

|----|--------------|-------------------------------------------------------------------|-----------|

|    | 6.1          | Overview                                                          | 73        |

|    | 6.2          | Input files                                                       | 73        |

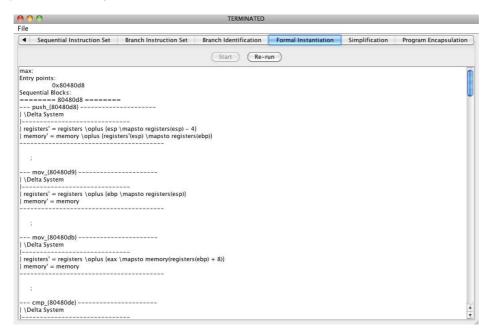

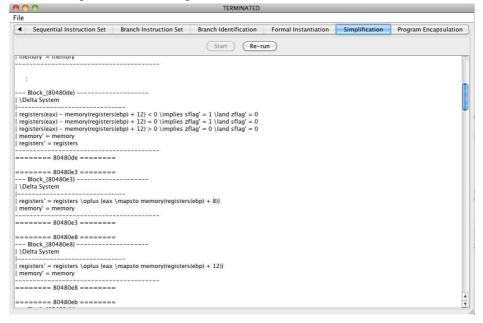

|    | 6.3          | Analysis stages                                                   |           |

|    |              | 6.3.1 Architecture                                                | 75        |

|    |              | 6.3.2 Branch identification                                       |           |

|    |              | 6.3.3 Formal instantiation                                        | 77        |

|    |              | 6.3.4 Simplification                                              | 78        |

|    |              | 6.3.5 Program encapsulation                                       |           |

|    | 6.4          | Output formats                                                    |           |

|    | 6.5          | Summary                                                           | 81        |

| 7  | Moo          | lel checking for verification                                     | 83        |

|    | 7.1          | Overview                                                          | 83        |

|    | 7.2          | System, requirements, and analysis                                | 83        |

|    | 7.3          | Z2SAL                                                             | 84        |

|    | 7.4          | Model checking Linear Temporal Logic properties                   | 87        |

|    | 7.5          | Model checking for fault detection                                |           |

|    | 7.6          | Summary                                                           | 92        |

| 8  | Vori         | fication by symbolic proof                                        | 95        |

| 0  | 8.1          | Overview                                                          |           |

|    | 8.2          | Symbolic proof in IsabelleHOL                                     |           |

|    | 8.3          | Converting Z to an Isabelle model                                 |           |

|    | 8.4          | Proofs of properties                                              |           |

|    | 8.5          | Proof assistant counterexamples for fault detection and tracing . |           |

|    | 8.6          | Summary                                                           |           |

| 0  | <b>T</b> 7   |                                                                   | 105       |

| 9  |              | fying a hardware usage requirement                                | 105       |

|    | 9.1          | Overview                                                          |           |

|    | 9.2          | A hardware interaction example                                    |           |

|    | $9.3 \\ 9.4$ | SAL verification                                                  |           |

|    | 9.4          | Summary                                                           | 110       |

| 10 | Con          | clusions                                                          | 111       |

|    | 10.1         | Software analysis                                                 | 111       |

|    | 10.2         | Future work                                                       | 112       |

| Bi | bliog        | raphy                                                             | 119       |

|    | _            |                                                                   |           |

| Α  | Flat         | tening CSP-OZ to pure Z                                           | 121       |

| в  | Der          | ived MaxInt CSP-OZ model                                          | 125       |

| С  | Max          | Int for import to Z2SAL                                           | 133       |

| D  | Max          | Int SAL file                                                      | 137       |

| CONTENTS |

|----------|

|----------|

| $\mathbf{E}$ | SAL suite counter example for brokenmaxint | 145 |

|--------------|--------------------------------------------|-----|

| $\mathbf{F}$ | Isabelle Z theory file                     | 153 |

| G            | Max example Isabelle theory file           | 155 |

| н            | Exdev SAL file                             | 163 |

х

## Chapter 1

# Introduction

## 1.1 Motivation

This work was prompted by the author's experiences with safety critical software projects in industry. Many good processes exist for ensuring the integrity of software. Some are verification techniques that seek to confirm that the software satisfies necessary requirements, others are development processes that are designed to minimise the creation of faults by ensuring that the programmers always have a clear idea of their objectives, and always have a clear understanding of the source code that they and other team members are writing. All of these techniques are valuable to software development, but many of the processes in use have limitations that prevent or complicate their application to software that interacts directly with hardware.

Many projects make use of static analysis to give a measure of assurance for the safe functioning of the code. Some of these analysis techniques measure a general software quality metric (such as conformance to a coding standard) to give an engineering estimate of its quality. This is often demonstrably very accurate and able to give a very high level assurance, but it lacks the mathematical certainty that is (at least philosophically) possible through the application of formal methods. Other techniques have a formal underpinning, particularly those that are based on "safe" language subsets. These use restricted versions of common programming languages to make the code completely statically determinable and so amenable to static analysis. The details of these languages are discussed further in §2.3 but the significant issue is that by restricting the language they necessarily make themselves unusable for applications that rely on the features that have been removed. One area that depends heavily on features that are often restricted or removed is hardware control. This will be the focus for the work presented here.

Hardware control and interaction is an area that is central to many safetycritical systems as they tend to be embedded systems or systems with a device control aspect. Many restricted languages remove any feature that interacts with the hardware, since these features reduce portability and prevent deterministic reasoning about the code without making assumptions about the behaviour of the hardware. However, in the case of device drivers it makes perfect sense to make assumptions about the hardware — a specification of the hardware's behaviour is always necessary if software is to be written to control it.

## 1.2 Objective of this work

The principle difficulties that current techniques face when verifying hardwaredependent software are:

- They have no way to statically determine the behaviour of code that interacts directly with the hardware.

- Current techniques are necessarily detached from the hardware (for instance language subsets, discussed in §2.3) or treat hardware in an abstract, general way (such as the heap model in Separation Logic §2.5.3).

- Verification must fit into an industrial workflow and not be overly dependent on expert skills, and must be applicable to large scale systems in reasonable time.

This work aims to produce techniques that use knowledge of the behaviour of specific hardware in order to allow the verification of its control software. More detailed background on verification in general, and the use of restricted language subsets is presented in §2. This work attempts to avoid the difficulties of analysing high level language code by taking the opposite approach — analysing code at the executable file level. While restricted languages attempt to make code sufficiently abstract that hardware details are irrelevant, the objective here is to make use of known hardware details to make high level language concerns irrelevant. The intention is to disassemble executables using a formal specification of their target architecture as a guide. This should produce an interpretation of the software based on the environment in which it will run and should provide a better basis for understanding its interaction with the hardware.

The principle contribution of this work is a technique for inferring a formal model of the behaviour of a hardware dependent system that has the following properties:

- The ability to represent the interaction of software and hardware components in the same model, and allow the verification of properties of hardware usage;

- a fully automatic implementation with no human input required after the submission of the hardware specification and the software for analysis;

- produces models of a size and complexity that can be understood by humans and is practical for the application of formal verification techniques;

#### 1.2. OBJECTIVE OF THIS WORK

• maintains traceability from the produced model back to the source program to support fault localisation and repair.

Along with solving the technical problem of analysing executable code using formal methods, this work will strive to produce techniques that can be automated wherever possible. Two common criticisms of working at the executable code level are that the sheer number of individual instructions make analysis difficult, and that the code is in a machine readable form rather than one intended for human understanding. By allowing automation of the labourious parts of the analysis it is possible to avoid both concerns, since computer systems are intended to handle large volumes of repetitive work, and no criticism can be made of using a machine to interpret machine readable data.

The potential for exploring the analysis of specific, complex assembly language and CPU detail was present at many stages of this work. Areas such as virtual memory addressing, multi-processor architectures, timing, and interrupts could each have been explored individually for the entire duration of the work. This exploration was eschewed in favour of developing a complete workflow that converts an executable to a formal representation with a focus on being applicable to industrial verification processes. This required certain assumptions to be made about the software and the execution environment. It is assumed that the target of this verification will be a high integrity embedded system in which the hardware and software design emphasises reliability over "rich" features, and all components of both the hardware and software system are under the control of the implementing organisation. This may not be direct design control, but it is assumed that the hardware and operating system components will be known, expected to be relatively static for the life of the system, and available for analysis.

Specifically, the analysis assumes that the virtual memory and execution environment of the program is correctly maintained. It assumes that the virtual address space is free of aliasing, and is predictable — so the value written to a location is the value that will be read subsequently unless it is explicitly altered by this program. Also, interrupts are ignored since it is assumed that the CPU will resume the program with the same environment as when it was interrupted. Where the interrupt mechanism alters hardware registers or something else that is observed by the program this should be represented in the hardware specification or in the verification properties.

These assumptions are not unreasonable, and can be considered in the framework of a layered process of system verification. The assumptions should be based on the verification of the CPU hardware, and of the operating system components that drive it — such as the interrupt handlers and the code that maintains the Memory Management Unit (MMU) control registers. Both of these are instances of highly hardware-dependent software they might well be the first elements of a system to be analysed and verified using the techniques presented here. Since it is usual for interrupt handlers to be executed without the possibility of being further interrupted it would be quite reasonable to use these assumptions when performing the verification of their behaviour. They could be verified against the property that they return the CPU to the interrupted program without altering its state, and so analysis of the remaining software could proceed with this as a well-founded assumption. Similarly, the operation of the MMU could be conducted on a system specification that models the interactions between the real address space and the virtual address space. The correct maintenance of the properties of the virtual address space could be verified and used as justification for the assumptions used analysing higher layer software.

Another assumption is that the structure of the software is static for the active life of the system. Self-modifying code is an interesting and active research area[23], but preventing the application of such ideas is an acceptable loss if an extremely high-integrity system is required. Similar arguments can be made about other complex system structures.

## 1.3 Thesis Outline

This document consists of ten chapters and eight appendices. These form five parts:

- §2 gives an overview of the background to hardware-dependent software verification and a review of relevant prior work.

- §3,§4, and §5 describe the analysis process that was developed by this work, including some theoretical work developed to support the analysis, and detail of the phases of the analysis workflow that converts an input executable into a formal model.

- §6 introduces the Spurinna package that implements this analysis process, §7, §8, and §9 describe some case studies that analyse small code samples and verify defined properties.

- §10 contains conclusions and discusses potential future work.

- The appendices contain materials that may be useful for reference when considering the analysis process. The contain the full text of the example formal models and the SAL and Isabelle files used in the verification examples.

## Chapter 2

# Background

## 2.1 Introduction

This section presents a literature review of the areas that are relevant to this work. After a general outline of the verification problem, the literature is presented in three areas, corresponding to the three elements needed for a verification process. Each section contains a brief summary of the use made of the material in this thesis. The selection and application of particular methods is described in detail in §3.

## 2.2 Verification

The aim of any verification process is to ensure that a system exhibits certain properties. What these properties are is one of the inputs to the process, and the choice of suitable property definitions to ensure general reliability is a large and complex subject that is outside the scope of this work. Once the properties have been selected the verification of these properties in a software system requires three phases of analysis:

- Code analysis A technique to determine how the software behaves.

- Modeling A language is needed to represent the behaviour at a level of abstraction appropriate to analyse the properties of interest.

- **Property verification** A process to check that the behaviour satisfies the required properties, and identify violations with information that can be used to correct the problem.

Different verification techniques will have a greater or smaller explicit emphasis on some of these phases, but they will all exist in some fashion. Even in manual code reviews the behavioral model will be encoded in the reviewer's notes and mental model, and the property verification technique will be the reviewer's approach to fault finding. The remainder of this chapter will give an overview of the work that already exists in each of these three areas, with the intention of identifying suitable building blocks for an analysis technique that can be applied to hardware dependent software.

## 2.3 Code analysis

## 2.3.1 Overview

The first phase of analysis — determining how the software behaves — is complicated by many factors. Sheer size and complexity of software can make it difficult to fully determine the behaviour of the system, but size and complexity can be countered with automation. A more critical difficulty in understanding the behaviour of a software system is the lack of clear semantic definitions for many of the most common high level languages.

C.A.R. Hoare wrote [35] that:

Computer programming is an exact science in that all the properties of a program and all the consequences of executing it in any given environment can, in principle, be found out from the text of the program itself by means of pure deductive reasoning.

Unfortunately, this is only true if the meaning of every statement in the text of the program has a well defined operation. Whilst most programmers operate on the assumption that they know what any given language element will do, their understanding often rests on a number of implicit assumptions. As an example, the C language has been in use for 40 years and multiple documents have existed as *de facto* and *de jure* standards. The book published by the language authors [41] was used as a standard in many areas; the American National Standards Institute released a standard in [11]; the International Standards Organization accepted the 1990 revision of ANSI C as a standard, and have since published an updated standard [38] that includes many features — such as inline functions that were available in compilers for several years. Although ISO C99 is largely accepted as the standard there is a very large variation both in the standard that a compiler implements, and the extent to which a compiler correctly implements the standard.

This multiplicity of standards and compiler implementations produces a situation where the exact behaviour of a program written in C cannot be determined with certainty, even if the entire source code is available. Different compilers may produce different executable code, or they may produce semantically different code for different target platforms. In many cases this is due to the flexible and platform-independent nature of the C language. Many features are deliberately and explicitly standardised as "implementation dependent" where the compiler authors are expected to chose the behaviour that will accomplish the rough specification of the behaviour in the way that is most efficient on the target platform. Compiler verification is also an open research area that has

#### 2.3. CODE ANALYSIS

had some successes [21] but is still not widely adopted, so even if the standard was well understood there would be no certainty that the compiler produced a correct implementation.

The implementation dependent choices in the standards highlight the platform independence of the C language as its advantage for general programming, but a significant problem faced where high integrity verification is required. The language is designed to be written with the user unaware of the exact nature of the system on which the program will run. This can be handled elegantly by language constructs that allow the programmer to specify intent and have the compiler select the optimal implementation. However, this can go wrong if the programmer makes too many assumptions based on the system he is using for testing, rather than the target platform, or if the compiler writer has assumed a different interpretation of the programmer's intent and optimises for that instead.

These assumptions about intent and implementation can have particularly drastic repercussions when the limits of the system are exceeded in some way. Attempting to use more memory than exists, assuming a particular layout of the content of structures in memory that is not replicated on a different platform, expecting certain devices to be "memory mapped" at particular locations which actually vary across architectures, and many other errors can occur as the result of assumptions made at different levels.

## 2.3.2 MISRA C

In an effort to reduce the uncertainty resulting from the C standards' implementation dependent aspects, the Motor Industry Software Reliability Association (MISRA) released a "restricted subset" of the C language. The MISRA-C [46] guidelines remove most of the features whose behaviour is implementation dependent or incompletely defined in the major standards. The guidelines also include various coding style guidelines that seek to eliminate code patterns that have seemingly obvious but practically indeterminate meanings.

The incrementation operators are a particularly good example. The C statement:

x = y++;

can be expected to assign to variable x the current value of y and then increment the value contained in y. However, the statement:

x = y++ / y++;

is legal C but will have a different behaviour depending on the compiler's evaluation choices. It could have the same semantics as:

x = y / (y+1); y = y + 2;

or as:

x = y/y; y = y + 2;

depending on exactly when the post-increment operator is evaluated. The MISRA-C guidelines ban the use of the increment operator inside compound statements, much to the chagrin of some of C programmers. Many other similar patterns are banned from MISRA-C compliant code.

The MISRA-C rules are usually implemented in the form of static analysis tools that check that code conforms to a coding standard. Tools such as PC-Lint[8] and LDRA testbed[7] can check conformity to the MISRA-C ruleset, as well as other coding standards, including user-supplied ones.

The dissatisfaction of some C programmers — notably those who aim for maximum semantic density in their code — highlights a key area of resistance to the uptake of language restrictions as a partial solution to software defects. By limiting the language features available to the programmer it can make programming more time consuming for the same semantics. However, this extra time is a result of requiring more explicit reasoning about the operations being performed. In some cases simply forcing programmers to think and explicitly write the operations they wish to perform can result in the identification of logical errors.

## 2.3.3 SPARK Ada

These problems are not exclusive to C. SPARK Ada begins with a similar approach to MISRA-C. The SPARK Ada language is a restricted subset of the Ada language that removes features that allow for indeterminate behaviour. SPARK Ada goes beyond simply eliminating things that are inadequately specified and also seeks to prevent errors that are caused by runtime dynamism. By requiring all collections to be finite and statically defined it is possible for static analysis tools to determine the total resource requirements of the program. This sort of information is vital for embedded systems with limited system resources.

The SPARK restrictions are similar to the MISRA-C rules in that they increase the burden on programmers, but in doing so force the programmers to think explicitly about their systems. The introduction to the SPARK Ada book [17] describes the approach:

Those familiar with the evolution of Ada 83 into Ada 95 will note that many of the facilities added in Ada 95 are not available in SPARK. This is almost inevitable because most of the new facilities in Ada 95 were added in order to increase dynamic flexibility – that is to give more flexibility at run time. But this is precisely what SPARK is not about; in order to prove that a program is correct, it is necessary that the dynamic flexibility be kept to a minimum.

Having restricted the language to allow meaningful static analysis, the SPARK system includes a suite of static analysis tools maintained by Altran-Praxis Ltd. [9]. To facilitate analysis SPARK Ada code is annotated with Ada comments that have a defined format that is read by the analysis tools. These annotations contain assertions about the attached Ada code that should be statically determined. The statements include explicit lists of imports and exports, and statements of derivations that show how the author perceives the posterior values of variables exported to be derived from anterior values of imports. The static analysis tools can check that only explicitly imported variables are used and only explicitly exported variables are written, so identifying any unintended side-effects that are possible in pure Ada. The dependency analysis checks the derivation statements to ensure that the values of exported variables cannot be influenced by unexpected sources.

In addition to this data flow analysis, the SPARK toolset can perform control flow analysis. Annotations describing pre- and postconditions of the code segments can be checked by analysis of the control flow graph of the program.

## 2.3.4 Hardware verification

The phrase "hardware verification" is used here to refer to the verification of properties of digital electronic systems, particularly those that compose to form the computer systems on which the software under analysis will run.

Verification has been applied to many classes of digital system, but CPUs are the most relevant to this work. Two examples of formally verified CPUs are VIPER and AMULET. The VIPER processor was developed in the 1980s with the intention of being an entirely formally verified processor to be used in high integrity systems. The design was formalised in Z [40] and later in HOL [49]. The development was performed at the Royal Signals and Radar Establishment, in Malvern and the processor was used in a number of Ministry of Defence applications. The AMULET project developed a verified ARM-based processor in 1993 [33]. The latest AMULET is AMULET3 [34]. The AMULET research group at the University of Manchester continues to develop formally verified hardware projects [53, 57].

In both of these cases, and others [31, 32, 19] the digital system is modelled and verified in a formal modeling language such as CSP, Pi Calculus, Z, or HOL. Understanding the working of the system on which software runs is important to understanding the operation of the software itself, but the practical scope of work possible requires this thesis to take a layered approach. Since the verification of hardware implementations of formal models is a mature subject this work will use a formal model of the computer system and its architecture as an input and assume that the verification of the real implementation is performed independently.

#### 2.3.5 Summary

Although MISRA-C, SPARK Ada, and related approaches make it possible to write high level programs that can still be properly analysed, they do so by making concrete the separation between the software and the system on which it runs. This approach is ideal for the vast majority of applications, where portability with semantic certainty is the key requirement. However, such an approach makes the direct hardware control applications that are the focus of this work impossible. Consequently, it will be necessary to avoid high level languages and all of the uncertainties that come with compilation. The desire to be independent of specific hardware is not present in the development of hardware control software, so the abstraction of implementation details to simplify understanding and portability across platforms is not relevant. Given that this objective is reversed, it is logical to reverse the approach taken by the language abstractions. Instead of trying to remove any requirement for knowledge of the target platform, this work will require a specification of the platform. This specification will be used to gain an understanding of the behaviour of the software on that platform.

Hardware verification is beyond the scope of this research, and is a wellunderstood field, so it will be assumed that an abstract representation of the system hardware is adequate. The nature of the representation will be discussed in §3 but it will operate at the level usually found in the instruction set reference documentation of the target processor. System features such as registers and memory locations will be modeled explicitly, but electrical and digital logic details will be abstracted.

## 2.4 Modeling

### 2.4.1 Overview

Once the behaviour of the software has been inferred its semantics must be documented in a notation that will best support the verification or refutation of the properties of interest. There are many different notations and languages for representing particular aspects of software behaviour, whilst deliberately abstracting others. This abstraction and simplification is necessary to allow the analysis to be computable in reasonable time, but also to allow the conclusions of the analysis to be comprehensible.

The selection of a formal modeling language largely depends on the nature of the properties that will be analysed. All formal languages emphasise some type of problem and their syntax is designed to write such problems clearly, whilst deliberately hiding other details behind abstraction. The correct choice of emphasis and abstraction is vital if the final model is to be readable, either by humans or by analysis tools. The criteria for readability are slightly different depending on whether human comprehensibility or machine processing are the objectives, but in both cases there is a need for succinctness: presenting the semantically critical elements in enough detail to allow meaningful understanding, but abstracting other elements behind the symbology so that the model elements are small enough to be handled easily.

Available tool support is another important criteria. The techniques for proving or falsifying properties are discussed in more detail in §2.5 but the availability of automated support for analysis will influence the choice of language.

## 2.4.2 The Z notation

The Z notation is described by Woodcock and Davies [61] as:

[...] based upon set theory and mathematical logic. The set theory used includes standard set operators, set comprehensions, Cartesian products, and power sets. The mathematical logic is a first-order predicate calculus. Together, they make up a mathematical language that is easy to learn and to apply. [...]

Z was originally proposed by Abrial et al. [14] and developed at the Programming Research Group at Oxford University. The ISO standard for Z was completed in 2002 [39].

Z allows simple axiomatic definitions of entities that are irrelevant to the specification being written, such as:

[Man] [Woman]

It then allows simple definitions in BNF and set theory:

$\begin{array}{l} Person ::= Man \mid Woman \\ Class == \mathbb{P} \ Person \end{array}$

The mathematical parts of Z are mainly contained in *schemas*. A schema contains two parts: variable declarations and predicates. *State schemas* define pieces of the system state, usually — but not necessarily — the state of discrete components.

| AdvancedAlgebra          |  |

|--------------------------|--|

| students: Class          |  |

|                          |  |

| $\#$ students $\leq 100$ |  |

This defines that the AdvancedAlgebra course contains *students*, which is of type Class — so is a set of *Person* items. Below the horizontal line is a predicate that limits the class size to 100 students. Schemas can be written on one line in a simpler form, so AdvancedAlgebra could be written as:

$[students : Class \mid \#students \leq 100]$

Another state schema might define the marks the students have obtained using a function:

\_AlgebraMarks \_\_\_\_\_ students : Class  $\begin{array}{c} marks : Person \rightarrow \mathbb{N} \\ \hline \forall s : Person \mid s \in students \bullet \\ s \in \text{dom } marks \end{array}$

The predicate here requires that there is a mark for every student. We can now perform *schema conjunction* on these two:

$MarkedAlgebra == AdvancedAlgebra \land AlgebraMarks$

This produces a new schema — here called *MarkedAlgebra* — that uses all the variables from both the conjunct schemas, and has a predicate that is the logical conjunction of the two predicates. Where variables in different schemas have the same name and type they are assumed to refer to the same thing. Other logical connectives, such as disjunction, are also possible. The conjoined schema in this case is:

| MarkedAlgebra                                |  |

|----------------------------------------------|--|

| students: Class                              |  |

| $marks: Person \rightarrow \mathbb{N}$       |  |

| $\#students \le 100$                         |  |

| $\#statems \leq 100$<br>dom marks = students |  |

| dom marks = students                         |  |

The other type of schema available in Z are *Operation schemas*. These specify how operations in the system change the state. They can define variables but more usually import state schemas for the parts of the system they alter or refer to. They are written in a pre- and post-condition form, with undecorated variable names referring to the state before the operation, and decorated variable names (e.g. x') referring to the state after the operation.

| AddMark                                          |  |

|--------------------------------------------------|--|

| $\Delta$ MarkedAlgebra                           |  |

| who?: Person                                     |  |

| $mark?:\mathbb{N}$                               |  |

| $who? \in students$                              |  |

| students' = students                             |  |

| $marks' = marks \oplus \{(who? \mapsto mark?)\}$ |  |

A number of features are illustrated here. Question marks on variables are a convention to indicate inputs. Exclamation marks are the convention for outputs. The Greek symbol  $\Delta$  is shorthand for bringing into scope all the contents of the state schema, as both before and after states — so every variable in *MarkedAlgebra* is brought into scope in both undecorated and decorated form. The predicate declaring that *students'* = *students* is important in Z, since unspecified post-conditions are not automatically considered unchanged

#### 2.4. MODELING

— they are considered unspecified, so an implementation is free to set them to any value. The symbol  $\Xi$  is shorthand for not only bringing into scope both decorated and undecorated forms of all variables in a state schema, but also including the predicate that their values are unchanged.

Finally, relations of all types are modeled as sets of pairs, where the first element is from the domain of the relation and the second is from the range. The  $\oplus$  operator is *overriding*, so the *marks* function is left unchanged except where the domain matches the domain of the second argument. Here the second argument is an anonymous function (i.e. set of pairs) with only one element: (*who*?, *mark*?), so only the value of *marks*(*who*?) is altered.

Operation schemas are usually instantiated by using renaming in the standard [x/y] form, where x is used in place of all occurrences of y. Operation schema can be composed in a number of ways, including sequential composition ( $^{\circ}_{9}$ ), conjunction ( $\wedge$ ), and disjunction ( $\vee$ ).

### AddMark[Bob, 75/who?, mark?] § AddMark[Jane, 92/who?, mark?]

This specifies performing the AddMark operation to give Bob 75 points, followed by performing the same operation to give Jane 92 points. The conjunction of the two operations would not be significantly different in this case as it would resolve to adding both marks simultaneously, but the disjunction would result in *either* Bob's *or* Jane's mark being entered. This is particularly powerful where the predicates are mutually exclusive, so the decision can be made by the conditions. For example  $[x, x' : \mathbb{N} \mid x < 30 \land x' = x + 1] \lor [x, x' : \mathbb{N} \mid x \ge 30 \land x' = 30]$  will increment x until it reaches 30, after which it will leave it unchanged.

## 2.4.3 B

The B formal method [12] is a state based specification language, with many similarities to Z (see §2.4.2). A critical difference to Z is that B is based around an explicit abstract machine model. The emphasis in the design of B was for a direct relationship to the implementation. This implementation based machine model simplifies the creation of tools for simulation and code generation.

Several extensions to B appeared around the time that this work was beginning. CSP||B [58] composes B and CSP in a similar way to CSP-OZ (see §2.4.6). Event-B [13] is an evolution of B to have a simpler syntax and a more heavily process driven style. Event-B has strong tool support from the Rodin suite [15].

## 2.4.4 CSP

Communicating Sequential Processes (CSP)[36] is a process calculus — that is, a language for specifying the behaviour of a system as a collection of processes that evolve separately but interact. In CSP the interaction is modelled through communication along defined *channels*. The evolution of a process can be guided

by its communication with other processes. More critically, the evolution of two processes can be *synchronised* by their communication. This synchronisation is the key element of CSP. It allows a simple and elegant abstraction to reason about many of the most fault-causing problems of distributed systems.

The CSP model contains *processes* and *events*. The most basic process evolution is *prefix*, where an event occurs and then the process evolves to a different process:

$$x \to P$$

This statement defines a process, so can be the target of a prefix evolution, which can itself be the target of an evolution, etc.:

$$a \to (b \to (c \to P))$$

The *STOP* process represents deadlock, and is used as the terminal process of all finite-trace models:

$$a \to (b \to (c \to STOP))$$

Processes can also be recursive:

$$P = x \to (y \to P)$$

The evolution of a process can also contain choices. These choices are defined as either *internal*  $(\Box)$  or *external*  $(\Box)$  choices. In the case of internal choice the decision is made entirely by the system and the environment cannot influence the choice. With external choice the decision is usually made by the environment precluding one path and allowing the other.

$$P = (x \to A) \sqcap (y \to B)$$

$$Q = (x \to A) \sqcap (y \to B)$$

In this example P and Q have different observable behaviours since Q will "allow" either event x or y to synchronise with it, whereas P will only allow one — and which one will be determined by the system at run time.

The notion of communication and synchronisation is central to CSP models. Where two processes are executed concurrently (which is defined using the || symbol) and their alphabets have an intersection they are assumed to require synchronisation on the shared events.

$$P = a \rightarrow (b \rightarrow P)$$

$$Q = b \rightarrow Q$$

$$System = P \mid\mid Q$$

14

#### 2.4. MODELING

In the process System the sub-process Q will not be able to evolve through the *b* event until the sub-process P is also ready to evolve with a *b* event. Since P requires an *a* event first, this forces the whole system to wait for an *a* event before either component proceeds past the *b* event. This simple syntax for representing synchronisation and inter-process control is the core of most CSP models.

The events are then enhanced to represent communications. Processes can input and output on *channels* using the ? and ! operators. The pipe operator >> directs the output from one process to the inputs of another:

$$P = a! v \to P$$

$$Q = a? v \to Q$$

$$System = P >> Q$$

This will pass an endless stream of values v from P to Q along the a channel.

Verifications on CSP models usually operate on traces in the systems. Verification techniques such as refinement measure possible traces, and refused events at different points in the traces. A process Q is a *traces refinement* of P if all the traces of Q are also traces of P. If P specifies the "safe traces" of a system then an implementation Q performing a subset of them seems reasonable. This is incomplete as a requirement system though, so *failures refinement* requires that the *failures* of Q is a subset of the failures of P. Failures are defined as a pair (s, X) where s is a trace that ends with an event X being refused. This models the behaviour that an implementation is allowed to refuse, and prevents the *STOP* process satisfying a requirement, even though its traces are a subset of any processes traces so it is always a traces refinement. Finally, *failures divergence refinement* adds requirements to identify and limit *livelock*, where a system may perform internal events but not produce any externally visible actions.

Failure Divergence Refinement (FDR) [44] is a software system designed to analyse CSP models. As its name implies it emphasises *failures divergence refinement*, as discussed in §2.4.4, and can also check the more general traces refinement and failures refinement properties. It is also capable of measuring other system properties, such as identifying potential for deadlock and livelock.

## 2.4.5 Object Z

Object Z[24] is an extension to the Z language (see §2.4.2) to add object oriented ideas such as classes, inheritance, and polymorphism. Object Z creates classes by collecting a Z state schema with a Z operation defining initialisation and some Z operation schemas to define the methods. Visibility notions similar to *public* and *private* in other OO notions are handled with a "visibility list" that identifies public and, implicitly, private methods. An example from [27]:

\_\_\_Memory[D]\_\_\_\_\_ 1 (INIT, Read, Write)

| m:A 	o D                          |

|-----------------------------------|

|                                   |

| m = arnothing                     |

|                                   |

| a?:A                              |

| d!:D                              |

| $a? \in \operatorname{dom} m$     |

| d! = m(a?)                        |

| Write                             |

| $\Delta(m)$                       |

| a?:A                              |

| d?:D                              |

| $m' = m \oplus \{a? \mapsto d?\}$ |

Inheritance is handled by including all the state and transition information but not the visibility list. Multiple inheritance is allowed and is modeled by simply including all of the content from the parents in any order. Schema with the same name are conjoined.

Instantiation of classes simply uses class names as variable types and then uses the dot notation for methods:

ct : Count [...] ct.INIT [...]

Object Z allows communication between classes using a CSP style || notation, so two methods can be parallel composed and then inputs and outputs with identical base names are matched.

| BankAcct                 |

|--------------------------|

| Withdraw                 |

| $\Delta(money)$          |

| $amount!:\mathbb{N}$     |

| money' = money - amount! |

| Deposit                  |

| $\Delta(money)$          |

| $amount?:\mathbb{N}$     |

| money' = money + amount? |

$\begin{array}{c} Transfer \\ from?: BankAcct \\ to?: BankAcct \\ amount?: \mathbb{N} \\ \hline from?.Withdraw(amount?) || to?.Deposit(amount?) \\ \end{array}$

## 2.4.6 CSP-OZ

CSP-OZ[30] takes the Object Z extension of Z (see  $\S2.4.5$ ) and extends it further by using the CSP process calculus (see  $\S2.4.4$ ) to add process-based control flow specification for the operations. A CSP-OZ class has a collection of CSP process in which the event alphabet is the Z operation schema names from the body of the class. The main process defines the entry point and the evolution of this CSP process specifies the allowed traces of operations that can occur on the class.

$\begin{array}{c} Printer \\ channel \ print : [p : PID] \\ channel \ card, nocard : [] \\ main : \ print?x \rightarrow (card \rightarrow main \sqcap nocard \rightarrow main) \end{array}$

## 2.4.7 Summary

The analysis process presented later in this work separates the inferred program behaviour into control flow and state change components. Consequently, it is ideal to represent the inferred behaviour in one of the languages that combines a process calculus with a state based language. Within reason, the choice of modeling language between Z and B is arbitrary. The B language has arguably greater tool support and its machine model makes many forms of symbolic execution and model checking easy to implement. However, this machine model is a core component of the language and this constrains all models to use at least this basic structure, even if an entirely different system model might make analysis more efficient or comprehensible. Z has no such constraints, being completely arbitrary system specifications and state change operation specifications. For this reason, and because of the author's prior experience and the Z community available in Sheffield, this work will use the CSP-OZ language for modeling. CSP-OZ allows the control flow components of the analysis to be rendered almost independently of the state change components, which simplifies the analysis and its implementation.

## 2.5 Property verification

## 2.5.1 Overview

Having inferred the behaviour of the system and modeled it in a formal language it is possible to assess whether the required properties hold, and if not it is desirable to produce counter-examples or other information that highlights the ways in which the system violates the properties.

There are a number of ways to establish whether a system's behaviour satisfies a property. The most general method is simply to test the system in a series of situations that have been designed to evaluate the property. Designing a suite of tests that is certain to identify all possible violations of the property is an extremely difficult task. Where the system has been formally modeled, and where the property is specified in a rigorous way it becomes possible to be more precise and complete with the test suite. The ultimate pinnacle of this approach is model checking. Where a system can be represented by a state model and a series of transitions it is possible to examine *every possible* trace of transitions from every possible state. If this can be accomplished, and if the model is an accurate representation of the system behaviour, then it is certain that the system satisfies the property, or that all failure situations have been identified. For systems of anything above trivial size this approach quickly becomes intractable. Since every possible state must be examined, along with every possible trace, a small increase in the potential state space creates an exponential increase in the search space — a problem known as state space explosion. For this reason most model checking is done with a complete transition system by a significantly simplified and abstracted state model. If the state model is chosen well then this does not need to impact the validity of the analysis. It is generally the case that system failures occur at critical values — division by 2 tends to imply that division by 3 will work, whereas division by 0 must be handled more carefully.

An alternative to model checking is a symbolic approach. If division by zero is to be avoided, for example, but all division operations occur within guarded code sections, then it is sufficient to demonstrate that the guards are such that it would be impossible to enter the code section with the divisor set to zero. This approach can produce powerful results since it is not computationally dependent on the size of the state space or of the model. The key drawback of symbolic proof is that anything beyond the more basic proofs requires a level of creative thought that has not been automatable. This forces the proofs to be performed manually, although various tools are available to simplify the proof process, provide feedback and verification of the proofs, and to tackle the simple proofs automatically once the proof condition has been imaginatively rephrased to be handled by machine.

As with formal modeling languages, different proof and analysis techniques are available for different classes of problems. They each have restrictions and abstractions that must be weighed when selecting a technique for a particular set of properties. The choice of CSP-OZ for the formal modeling language was partly influenced by the possibility of easily translating the produced models to emphasise the components necessary for particular analysis techniques.

## 2.5.2 Hoare logic

What is now known as *Hoare Logic* or *Floyd-Hoare Logic* was presented in the paper titled "An Axiomatic Basis for Computer Programming" [35]. The intention of the work was to present a method for performing deductive reasoning about the properties of a program. To do this it was necessary to introduce the axioms that describe the behaviour of the basic components of computer programs.

The paper begins by describing the rules for computer arithmetic — especially highlighting the differences from conventional mathematics' version of arithmetic, such as value overflow. It then proceeds to present axioms for the operations in a pseudocode language that contains elements common to all imperative programming languages. The axioms are presented in the form of *Hoare triples*, which contain a *precondition*, the pseudocode statement, and a *postcondition*.

## $P{Q}R$

Here P is the precondition predicate, that specifies the conditions that must hold if the defined operation is to occur. All the axioms of Hoare Logic have this form, which is known as an *Hoare triple*; division is only properly defined if the divisor is non-zero, for example. Some axioms are universally applicable and so have the precondition **true**. Q is the program statement in pseudocode. R is the postcondition, which is a predicate defining what can be relied upon to be true after executing this statement, assuming that the precondition is satisfied.

The first axiom is for assignment:

$\vdash P_0\{x := f\}P$

where x is a variable identifier; f is an expression;  $P_0$  is obtained from P by substituting f for all occurrences of x.

This pattern of defining preconditions as transformations of the postcondition is repeated for the other axioms and reflects the predicate transformation semantics that underlay the system. It allows useful reasoning about the behaviour of the whole program by eventually representing the operation of the program as a transformation of the expected postcondition into the precondition. Verifying properties then requires proving that the properties are guaranteed by the postcondition predicate, and then assessing the limitations implied by the precondition. Errors in the program are usually manifest as unexpected preconditions (x > 4 or something equally strange) that highlight unanticipated dependence on properties of the inputs.

The next axioms are the Rules of Consequence:

$$If \vdash P\{Q\}R \text{ and } \vdash R \supset S \text{ then } \vdash P\{Q\}S$$

$$If \vdash P\{Q\}R \text{ and } \vdash S \supset P \text{ then } \vdash S\{Q\}R$$

and the Rule of Composition:

If

$$\vdash P\{Q_1\}R_1 \text{ and } \vdash R_1\{Q_2\}R \text{ then } \vdash P\{Q_1; Q_2\}R$$

These rules allow for a program to be built from a sequential composition of operations, as is the case in almost all imperative programming languages, and allow for the satisfaction of following preconditions to be determined by components of preceding postconditions.

The final rule covers the other major class of imperative programming language construct: *iteration*. The *Rule of Iteration* is presented as:

If  $\vdash P \land B\{S\}P$  then  $\vdash P\{\text{while } B \text{ do } S\} \neg B \land P$

This defines some guard condition B that determines the limit of the iteration, and some *loop invariant* P that is always true during the execution of the loop. Generally, the loop invariant is phrased so that it guarantees some property of the elements that have been iterated over, or the value of some variable derived from the iteration steps.

Although not mentioned in this paper, the axioms of Hoare logic also include a *conditional rule*:

$If \\ \vdash P \land B\{S\}P \text{ and } \vdash P \land \neg B\{T\}P \\ then \\ \vdash P\{if B then S else Y endif\}Q$

Subsequent work would eventually reverse the bracket notation to enclose the predicates at either side of the statement:  $\{P\}Q\{R\}$  and to add a loop variant to the iteration rule that must decrease to guarantee termination.

Once the axioms have been established it is possible to prove properties of programs by chaining the rules together. The post condition of a preceding element can be used to show that the precondition of a succeeding element is satisfied, and so certify its postcondition to be used to satisfy a following element's precondition, and so on. Although Hoare logic axioms are defined over pseudocode elements, it is generally possible to rephrase any imperative language program into these basic components.

Since its publication, Hoare logic has been applied to a wide range of verification tasks, on languages as disparate as Java[59] and Z [29]. The application of pre- and postconditions and invariants that was pioneered by this work has formed the foundation of verification techniques such as SPARK Ada (discussed in §2.3.3) and Spec#[18]. It has been applied to compiler verification [21] and has been extended to accommodate extra analysis features, such as those presented in Separation Logic discussed in §2.5.3.

## 2.5.3 Separation logic

Separation logic is an extension to Hoare logic [35] that supports reasoning about programs that alter data structures. Reynolds [51] first suggested extending Hoare logic to include an operator to conjoin two propositions that depend on distinct areas of storage. Ishtiaq and O'Hearn [37] then used the Logic of Bunched Implications [47] to extend Reynolds ideas and first began using the \* and \* operators. The ideas were then clarified in [48], which saw many of the definitions and axioms of Separation logic defined. A more detailed semantic analysis followed in [62].

### Intuitionistic Reasoning about Shared Mutable Data Structure [51]

This paper extends Hoare logic "to deal with programs that perform destructive updates to data structures containing more than one pointer to the same location". The key concept is what the paper calls "independent conjunction". It uses the & operator — which is superseded by \* in later Separation Logic papers — to produce syntax such that P&Q holds only when P and Q hold and depend on disjoint areas of storage.

The model defined here has a value as *either* an integer, an Atom, or a Location, with these sets disjoint and countably infinite. The possible stores and heaps are defined as:

$Stores_V = (V \rightarrow Values)$  Where V is a finite set of variables  $Heaps_L = (L \rightarrow Values^+)$  Where L is a finite set of Locations

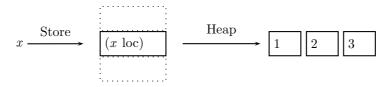

The paper uses a style similar to LISP [45] to represent constructing new variables. It uses **cons**<sub>1</sub>, **cons**<sub>2</sub>, **cons**<sub>3</sub>, etc. to construct sequences of items on the heap. So  $x := cons_3(1, 2, 3)$  will create a new entry in the heap function that maps some unique location to the sequence of values 1, 2, 3 and then updates the store so that x is mapped to this location. Figure 2.1 shows this relationship diagrammatically.

Figure 2.1: An example of the **cons** operation

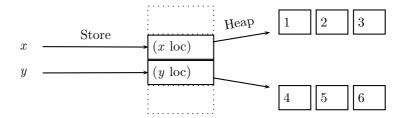

This differs slightly from the normal programming model of referencing since the sequence 1, 2, 3 is not, itself, in the same store as the location. In C - and in actual implementations of all languages - reference locations are data values in the program's memory space, just like the values to which they refer. Also, the collections of values that are referred to by the Heap function are not subsets of a contiguous store but are independent sets. Consequently, in this model, there is no way to represent offsets to Locations. If  $x \mapsto a, b, c$  were in the Heap it is not implied in this model that  $x + 1 \mapsto b, c$  since x + 1 is an entirely separate entry in the domain of the Heap function. Figure 2.2 shows this diagrammatically.

Figure 2.2: The **cons** operation producing disjoint sets

Altering the model to better capture realistic behaviour of offsets was one of the significant additions by O'Hearn et al. [48].

The paper introduces the use of a comma separated list into its system of propositions to represent the condition that holds after the use of **cons** described above. So it is now possible to produce some Hoare logic assertions:

$$\{P\} \quad x := \mathbf{cons}_n(E_1, ..., E_n) \quad \{P\&(x \to E_1, ..., E_n)\}$$

Later separation logic papers update this both the Heap model and the proposition to better represent the notion of sequential locations used in real systems.

This, with a few other straightforward definitions, allows the style of Hoare logic definitions and statements that will be used throughout Separation Logic. The paper ends with a partial correctness specification — that is, the series of Hoare logic assertions between the statements of the program — for a program that deletes zero value elements from a doubly linked list.

#### 2.5.4 IsabelleHOL

Higher Order Logic is a branch of mathematical logic, but in this context it refers to the proof assistance systems developed at the Automated Reasoning Group in Cambridge. The original HOL systems were designed for verifying hardware, as discussed in §2.3.4. Isabelle is a related proof assistant developed by the same group for more general logical reasoning [1].

Proof assistants work by allowing the user to present proofs in a particular logical system and the assistant checking that the proof is a correct application of the logic's rules. HOL and Isabelle support a large range of logic systems, both higher order and first order. Systems produced for Isabelle include Hoare Logic, Zermelo-Fraenkel set theory [16], Z [43], and B [25].

A *theory* in Isabelle is a collection of datatypes, functions, and definitions, along with proofs of theorems over these. A theory begins by importing a

suitable logic system. This imports all of the basic rules of the selected system, which can then be used in the definitions.

```

theory Test

imports Datatype

begin

datatype 'a list = Nil ("[]")

| Cons 'a "'a list" (infixr "" 65)

primrec app ::

"'a list => 'a list

=> 'a list" (infixr "@" 65)

where

"[] @ ys = ys" |

"(x # xs) @ y = x # (xs @ y)"

primrec rev :: "'a list => 'a list"

where

"rev [] = []" |

"rev (x # xs) = (rev xs) @ (x # [])"

```

Having created definitions it is possible to write *theorems* and *lemmas* that encode properties of the definitions. These can then be proven by referencing the definitions and rules from the imported logic. Isabelle contains a number of automated tactics that will attempt to apply certain common patterns of rules to achieve a proof.

```

lemma app_Nil [simp]: "xs @ [] = xs"

apply(induct_tac xs)

apply(auto)

done

```

Additionally, Isabelle contains a package called *sledgehammer* [52] that will automatically convert the theorem and the definitions into the correct input formats for a range of external automated theorem provers and SMT solvers, which are then run to attempt to find proofs. There are also the *nitpick* [20] and *refute* [60] counter example generators that attempt to find descriptive counterexamples to the theorem if it is false.

IsabelleHOL has been used successfully in the verification of various systems [42], and has been incorporated as the backend to a software analysis system [22].

## 2.5.5 SAL

The Symbolic Analysis Laboratory (SAL [4]) is a suite of tools for performing analysis on state machine models. The tool suite includes a simulator, a deadlock checker, a symbolic model checker, a bounded model checker, and a counterexample finder. The SAL input language [26] is common to all of the tools and there is a large community creating new tools that all use the common input language.

The SAL input language requires all types to be finite, but then supports finite sets, triples, subranges, arrays, records, total functions, modules, and recursive definitions. The state machines are defined with a collection of state variables and an initialisation, and then a collection of transitions. The syntax for the operations includes conditions on the state that control when the transition can be traced. The effect of the operation on the system state is defined using anterior and posterior variables, with the posterior variables identified with a prime symbol (') in a similar way to the Z notation (see §2.4.2).

The simulator allows a machine to be loaded and transition paths to be explored. The deadlock checker analyses the transition conditions to detect potential states from which no transition will be possible. The SAL language allows for an *ELSE* transition that is always available, which can deliberately remove the possibility of deadlock, but for meaningful deadlock analysis this should be omitted.

The model checkers can check properties written in Linear Temporal Logic (LTL) or Computation Tree Logic (CTL) forms. The symbolic model checker compiles the definitions into optimised binary decision diagrams (BDDs) and simulates models using Buchi automata. The bounded model checker uses the SMT solver *yices*[10], which was also developed at SRI.

## 2.5.6 Z2SAL

The Z2SAL[28] project has developed an automated system for converting Z specifications (see §2.4.2) into the input language of the SAL suite (see §2.5.5). The parser and translation system currently only works for pure Z, and not derivatives such as Object-Z or CSP-OZ. However, within this limitation it is possible to automatically translate entire Z specifications into SAL state machine models.

The process assumes that a Z state schema defines the system state, and a Z initialisation schema provides the details of the state initialisation. Thereafter, all Z operation schema are converted to transitions in the SAL model. The output SAL model is then available immediately for modelchecking against suitable LTL or CTL property specifications. The translation has the distinct advantage of retaining the names of state variables and operations as variable names and transition names respectively in the SAL model. This, coupled with the innate similarity between the anterior/posterior variable conventions between Z and SAL means that users familiar with the Z model can easily read the SAL model. This is of critical importance when errors are detected as they can quickly be traced back to the original Z specification. This makes the use of Z2SAL with the SAL model checkers a very easy and powerful technique for exploring temporal logic properties of a specification.

## 2.5.7 Summary

All of the techniques surveyed here could be applied to executable files that control hardware. In all cases it is possible to translate either CSP-OZ or one of its sub components into the form necessary for the analysis. Different analysis goals will necessitate different approaches, and this work deliberately takes no position on which technique should be applied. If any technique were favoured it would be easy to question the need to render the model to CSP-OZ and then convert, instead of rendering the model directly into the input language of the analysis technique, but this generalism was precisely the objective in the selection of CSP-OZ and in the efforts made in §3.3 to ensure that both the control flow and state transition features are rendered as fully as possible.

Time limitation prevented extensive case studies of verification, but the availability of the Z2SAL tool [28] made this an ideal example, the results of which are presented in §7.

# Chapter 3

# The proposed solution

# 3.1 Introduction

As described in §1, the aim of this thesis is to develop a technique to verify properties of high integrity software systems that interact directly with hardware. This chapter presents the design decisions that were made to produce an analysis process to achieve this goal. The decisions in choice of code analysis technique, modeling language, and verification approach were made with particular emphasis on the three principle objectives of this work:

- Analyse software that depends on hardware behaviour

- Handle large instruction count or large quantities of fine detail

- Produce results that are comprehensible and provide traceability between the results and the original code.

As identified in §1.2, the target for this work is high integrity embedded systems where the engineering team can be expected to have more control over the low level system components than might be the case in a more general software system.

# 3.2 The analysis process

The hardware dependence will be countered with reference to supplied specifications of the hardware behaviour. Given that the target domain for this work is software elements that are designed to provide hardware control or interaction it is reasonable to make the interaction of the software with the hardware the core of the analysis and the produced behaviour model. For the reasons discussed in  $\S1.2$  the analysis will be performed on executable files.

Because executable files potentially contain millions of instructions even for relatively small software subsystems it is important that scalability and automation be highly prioritised in the design of the analysis methodology. This is handled by presenting the specifications in machine-readable form and then creating an entirely automated analysis work-flow that requires no human interaction.

With the absence of human interaction in the analysis process it is important that the eventual results are not totally divorced from the input materials. Identifying property violations is only useful if it is combined with enough traceability information to allow the problem to be localised in the source code and corrected. Additionally, the presentation of the analysis results must be clear and reasonable enough to be understood by a developer of the source program, rather than exclusively by expert users of the analysis technique. These conditions seem competitive since the greatest hurdle for comprehensibility will be the sheer number of instructions, whilst traceability requires that exact information be kept about the source of a particular model element.

Most executable files — especially, but not exclusively, those compiled with debugging information — contain considerable *symbol* information with function names and other readable information derived from the high level language. This information will be retained in the formal model to allow easy and comprehensible linkage to the source. The programmatic structure will also be retained as the model will encapsulate program elements at the function level, which on most architectures is clearly defined and used by compilers to implement functions (or their equivalents) in the high level language. Finally the virtual address of the instructions that are modeled by a particular formal model component will be retained as a subscript to the name. After the simplification stage (described in detail in §5.4) these will be collected into address ranges but they will still identify small and programmaticly self-contained sections of the source executable.